어떻게 해야 Cache의 성능을 높일 수 있을 지에 대한 논의를 하는 강의

Interleaved Memory Memory Interleaving 용어 새로 등장!!

데이터가 왔다갔다 하는 것을 Bus라고 얘기한다.

32인승짜리 버스가 있다고 생각할 수 있다.

메모리에서 Cache로 가는 시간이 오래 걸리기 때문에 한 꺼번에 많은 데이터를 보내면 성능을 높일 수 있을 것이다.

128인승짜리 버스를 타고 보내면 훨씬 빠른 Access가 가능하다.

좋긴 좋지만 문제는 돈이 많이 드는 문제점이 있다. 돈을 생각하지 않고 넘어갈 수 없기 때문에 좋은 방법이긴 하지만 가격이 많이든다

Interleaved Memory

CPU가 주소를 issue한다. 10번지에 있는 데이터!! 메모리에 가서 10번지를 찾는다.

메모리를 각각 여러개로 나눠서 10번지에 해당하는 메모리에 해당하는 데이터를 보내는 것을 Interleaved Memory라고 한다.

1 cycle: sending address

15 cycle: reading one word data

1 cycle: sending one word data

1)

1 (CPU에서 Cache로 주소를 보내는 시간)

+ 4 word가 있으므로 15cycle이 걸리는 것을 4번 반복하게 된다.

+ 다시 CPU로 4 word를 보내므로 총 65 cycle이 된다.

2)

1 + 15 + 1이면 된다. 4word가 한꺼번에 오도록 만들 수 있지만 비싸다.

3)

주소를 보내는 1cycle

각각의 10번지의 데이터를 준비시키고 (동시적으로 일어난다) 15 cycle이 걸리고 메모리에서 데이터를 가져올 때는 4개의 데이터가 하나씩 전달 되므로 4 cycle이 걸린다. => 22 cycle

4개의 bank로 만들어서 각각 메모리가 데이터를 준비해서 보내도록 만들어준 하드웨어 변경밖에 없다. 비싼 것을 사용할 필요 없이 4개의 bank로 만들어 17에서 20으로 떨어진 감이 있지만 가격적인 면에서 더욱 효율적이다.

어떤 Block은 반드시 Cache의 요자리에 들어가야 된다라는 것이다. (학번 나누기 도서관 의자의 개수의 방식으로 들어간다라는 것) 그래서 Fully associative를 쓴다. 빈 곳이 있으면 아무데나 들어갈 수 있는 방식이다.

Set associative란?

1 열람실에는 전전학생, 2 열람실에는 생명학생.. 등등으로 나누는 것. 열람실은 정했지만 빈 자리가 있다면 아무데나 앉아도 된다는 것 즉 해당 공간에는 들어가야 하지만 빈 곳이 있다면 들어갈 수 있다는 것이다. Direct와 Fully 의 중간 방식이 될 것이다.

Direct Mapped

index에 따라서 Block offset에 해당하는 데이터. Tag도 맞고 Valid한 데이터를 가져오고, Block offset에 해당하는 데이터를 빼내게 된다.

Fully Associate

Index가 없다. 어떤 한 곳을 정하는 것이 아니라 아무데나 들어갈 수 있다. Tagd와 Block offeset과 byte offset으로 이루어져 있다. block은 Cache의 어느 곳이든 들어갈 수 있다. 특정한 block이 있는지 찾으려고 Cache에 가게 되면 어디에든지 있을 수 있으니까 Cache의 모든 위치를 뒤져야 찾을 수 있다는 단점이 있다. 그러면 어떻게 찾는가 내가 찾으려는 Tag와 Fully Associate의 Tag를 Parallel하게 비교한다. 만약 Sequential하게 비교하게 되면 최악의 경우 없을 때 너무 많은 시간이 소요된다. parallel 하게 비교하기 위해서는 특수한 메모리를 사용해야 한다. (비싼 메모리가 사용된다. 그 메모리를 Associative Memory라고 부른다. 구조 자체가 다름. 동시에 Tag를 비교할 수 있게 만든다라는 것만 알고 있기로 함)

Set Associative

비어 있는 곳이 있으면 들어갈 수 있다. Cache의 block의 개수가 아니라 set의 개수로 나눠준다. 그리고 해당하는 곳의

비어있는 곳에 아무데나 들어갈 수 있다.

아주 디테일한 것까지 요구하지는 않겠습니다...ㅎㅋㅎㅋ

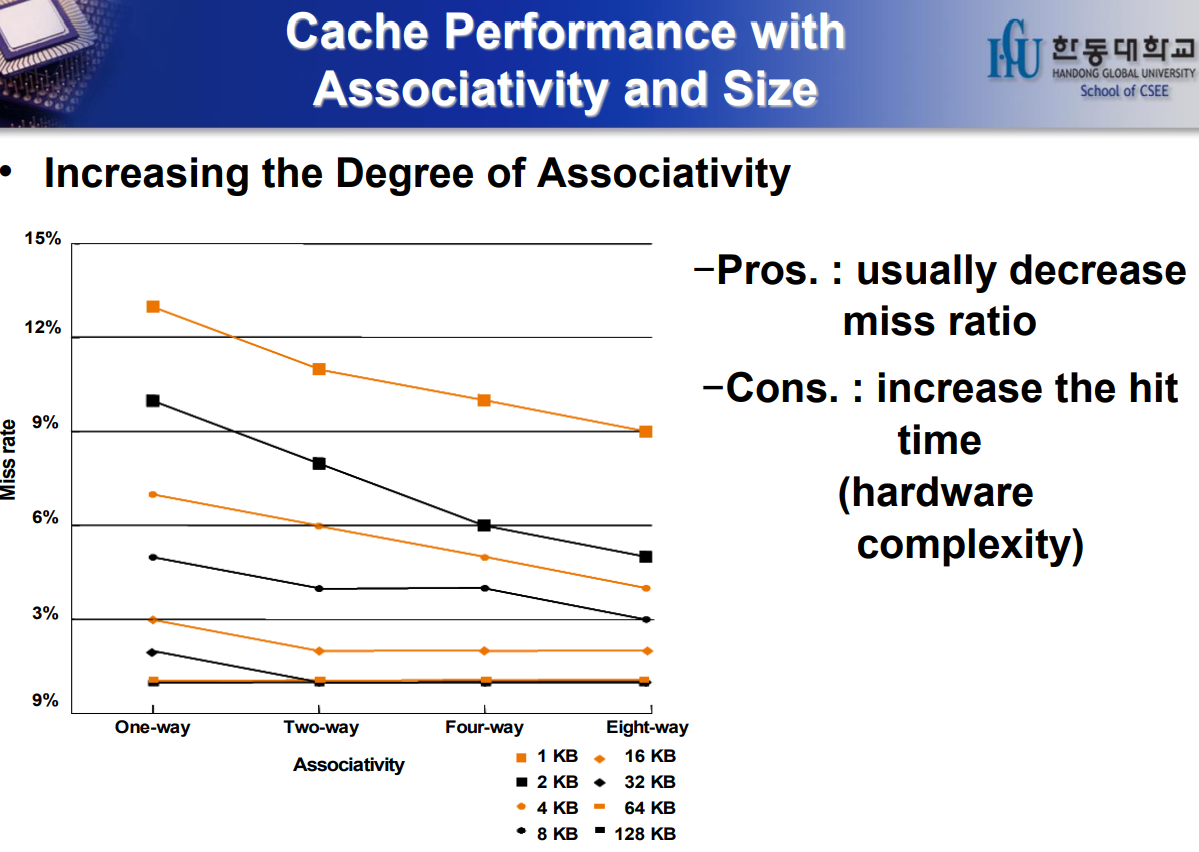

어느것이 가장 좋을까? miss rate가 줄어드는 것이 좋겟다. 일반적으로 Fully Associativity가 성능이 좋다고 할 수 있다.

단지 생각할 것은 hit time (동시에 Tag를 비교할 수 있는 것을 만들어야 하므로 hardware의 complexity가 늘어날 수도 있다.)

'🚗 Major Study (Bachelor) > 🟩 Computer Architecture' 카테고리의 다른 글

| 컴퓨터 구조 CH5_Virtual Memory (0) | 2021.12.06 |

|---|---|

| 컴퓨터 구조 5_Cache Performace (0) | 2021.12.01 |

| 컴퓨터 구조 5_Cache Performance (0) | 2021.12.01 |

| 컴퓨터 구조 5_Cache Memory (0) | 2021.11.29 |

| 컴퓨터 구조 5_Cache Memory (0) | 2021.11.29 |